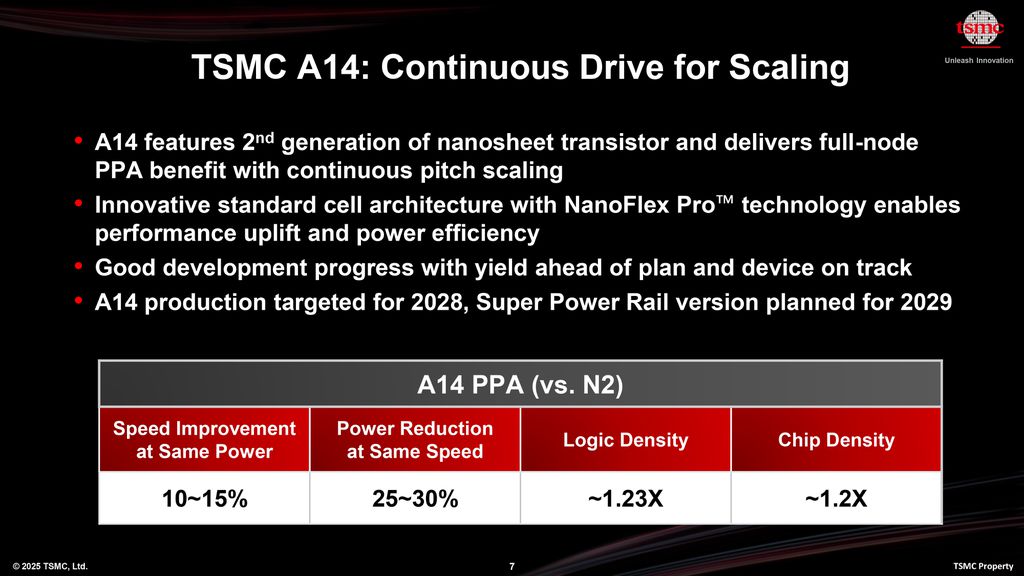

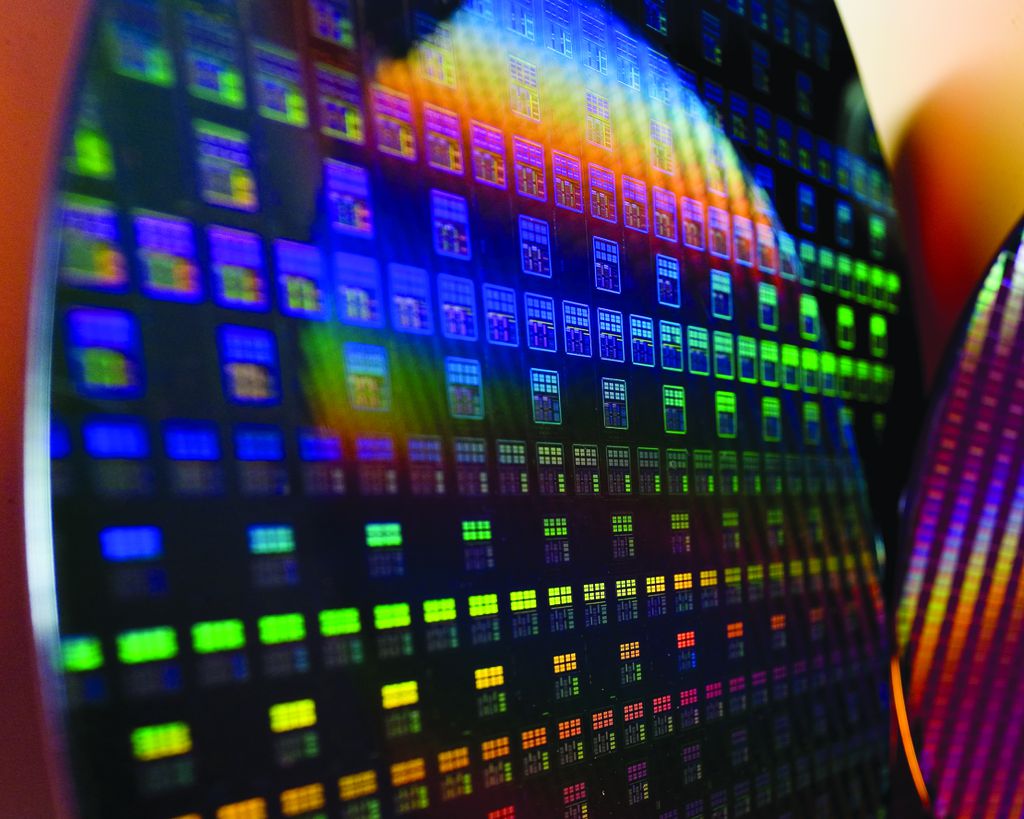

A TSMC anunciou nesta quarta-feira (23) seu novo processo de fabricação de semicondutores. Batizado de A14, o processo para a litografia de 1,4nm promete incrementos substanciais de desempenho (até 15%), eficiência energética (30%) e densidade de transistores (1,23x) em comparação com o atual nó N2 de 2nm. A companhia revelou que a nova tecnologia é baseada na segunda geração de Gate-all-Around (GAA) nanosheet e deve entrar em produção em massa em 2028.

- Intel deve usar litografia de 2 nm da TSMC nas CPUs Nova Lake

- TSMC anuncia investimento de US$ 100 bi para construir 5 fábricas nos EUA

A revelação aconteceu durante o North America Technology Symposium, em Santa Clara, Califórnia, principal evento anual da fabricante taiwanesa para clientes e investidores. Segundo Kevin Zhang, vice-presidente sênior de desenvolvimento de negócios e vendas globais da TSMC, o A14 representa “uma tecnologia muito, muito substancial”, sendo o próximo salto full-node no roadmap da companhia após os processos N2 e N2P.

A miniaturização dos transistores é o que sustenta a evolução dos processadores modernos, permitindo que fabricantes como Apple, AMD e Intel entreguem chips cada vez mais potentes e eficientes a cada nova geração. Com o A14, a TSMC demonstra mais uma vez sua capacidade de manter viva a Lei de Moore, que prevê a duplicação do número de transistores em um chip a cada dois anos, mesmo diante dos crescentes desafios físicos da escala nanométrica.

–

Entre no Canal do WhatsApp do Canaltech e fique por dentro das últimas notícias sobre tecnologia, lançamentos, dicas e tutoriais incríveis.

–

Nova tecnologia em fases: primeiro sem backside power delivery

O cronograma de implantação da litografia de 1,4nm será dividido em etapas. Na primeira fase, prevista para 2028, o A14 ainda não contará com a tecnologia de backside power delivery (BPD), também conhecida como Super Power Rail (SPR). Esta versão inicial será destinada a aplicações que não necessitam desse recurso avançado de distribuição de energia.

Isso significa que, inicialmente, o A14 manterá a distribuição de energia tradicional pelo lado frontal do chip, método mais do que adequado para a maioria das aplicações cliente, edge e especializadas que não demandam uma entrega de energia tão densa.

Já para 2029, a TSMC planeja lançar uma variante do A14 que incorporará o SPR, que transfere as linhas de distribuição de energia para o lado posterior do chip, liberando espaço no lado frontal para mais transistores e interconexões lógicas. Essa segunda versão deverá atender às necessidades de clientes que desenvolvem aplicações de alto desempenho para data centers e inteligência artificial, onde a densidade de energia é crucial.

NanoFlex Pro: a vantagem competitiva da TSMC

Um dos grandes diferenciais do processo A14 será a introdução da tecnologia NanoFlex Pro. Trata-se de uma evolução da atual arquitetura NanoFlex, permitindo às fabricantes de chips flexibilidade inédita para ajustar configurações de transistores e otimizar desempenho, consumo e área de acordo com necessidades específicas.

“A tecnologia também conta com nosso NanoFlex Pro, uma co-otimização para design de tecnologia (DTCO) que permite ao designer criar seus produtos de maneira bastante flexível, alcançando mais benefícios de performance e energia”, destacou Zhang. Esta abordagem de design-technology co-optimization (DTCO) é uma vantagem significativa para os clientes da TSMC.

Enquanto a versão atual do NanoFlex já permite que fabricantes misturem e combinem células de diferentes bibliotecas (alto desempenho, baixo consumo, eficiência de área) dentro de um mesmo bloco, o NanoFlex Pro possivelmente oferecerá controles mais granulares sobre células individuais ou até mesmo transistores. Isso permitirá uma personalização ainda mais precisa do chip para diferentes cargas de trabalho, resultando em produtos mais equilibrados em termos de desempenho e eficiência energética.

Impacto e benefícios para a indústria e consumidores

Para fabricantes como Apple, AMD e Intel, o A14 possibilitará o desenvolvimento de chips com maior poder computacional sem aumentar o consumo de energia — ou até mesmo reduzindo-o. Isso é de extrema importância neste momento, com a indústria de semicondutores enfrentando desafios para atender à crescente demanda por processamento de IA sem elevar proporcionalmente o consumo energético.

Na prática, consumidores poderão ver os benefícios em várias frentes: smartphones com mais desempenho de IA on-device e maior duração de bateria; PCs mais rápidos e eficientes; data centers com maior capacidade de processamento e menor pegada de carbono. A redução de 30% no consumo de energia em comparação com o nó N2 é especialmente relevante para dispositivos móveis, que são limitados por sua capacidade da bateria.

Vale ressaltar que os chips baseados em A14 só devem chegar aos consumidores anos após o início da produção em massa em 2028. No caso da Apple, por exemplo, a empresa ainda utiliza o processo de 3nm nos chips dos iPhones atuais, e provavelmente só adotará a tecnologia de 2nm daqui a algumas gerações. Seguindo essa lógica, podemos esperar que os primeiros dispositivos com chips de 1,4nm cheguem ao mercado por volta de 2029 ou 2030.

Roadmap da TSMC e situação dos concorrentes

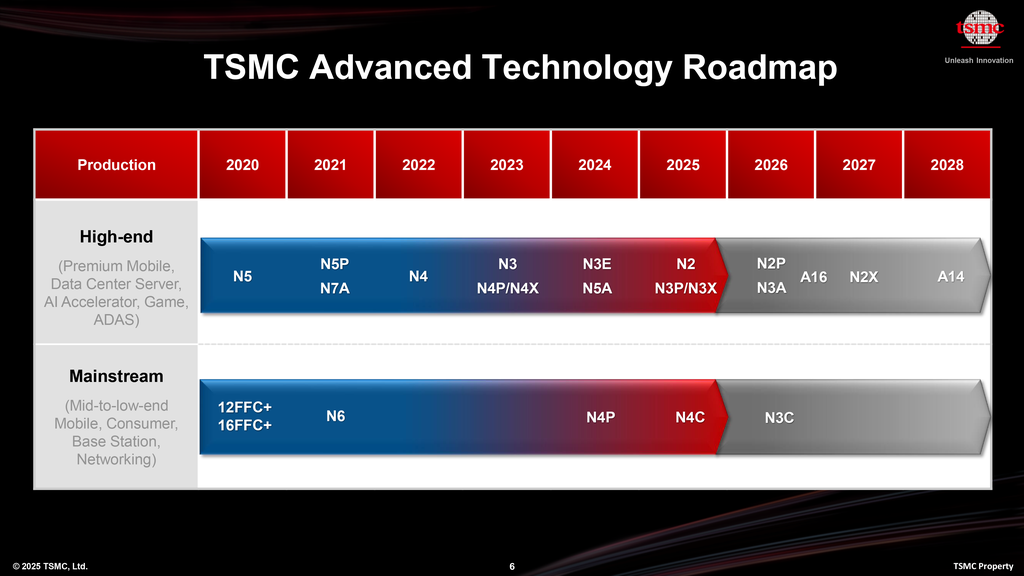

A revelação do A14 reafirma o roadmap de inovação ambicioso da TSMC para os próximos anos. Atualmente, a companhia fabrica chips em seu processo N3 (3nm), com versões aprimoradas como N3P previstas para os próximos lançamentos. O N2 (2nm) deve ter sua produção iniciada ainda em 2025, seguido pelo N2P e A16 (1,6nm) em 2026, abrindo caminho para o A14 (1,4nm) em 2028.

Além dos avanços em litografia, a TSMC também anunciou novidades em tecnologias de empacotamento de chips. A empresa planeja trazer para produção em massa, em 2027, sua tecnologia Chip on Wafer on Substrate (CoWoS) com tamanho de 9,5 retículos, permitindo a integração de 12 ou mais stacks de memória HBM junto com lógica avançada. Na mesma linha, apresentou o SoW-X, uma solução baseada em CoWoS para criar sistemas do tamanho de um wafer com poder computacional 40 vezes maior que as soluções CoWoS atuais.

Enquanto isso, a concorrência enfrenta desafios para acompanhar esse ritmo. A Samsung, principal rival da TSMC na fabricação de chips avançados, recentemente cancelou seu próprio processo de 1,4nm por razões não divulgadas. Em vez disso, a empresa sul-coreana formou uma equipe dedicada ao desenvolvimento de chips de 1nm, com objetivo de produção em massa para 2029 — prazo muito próximo ao que a TSMC planeja para seu 1,4nm, o que pode intensificar a competição nessa faixa.

Leia mais no Canaltech

- Rendimento da litografia Intel 18A é baixo e gera prejuízos à empresa

- Fundador da TSMC conta por que iPhones não tem chips Intel

- O que é o índice de aproveitamento dos wafers de silício?

Leia a matéria no Canaltech.