As arquiteturas CISC e RISC se referem a quão complexas são as instruções (comandos) que os CPUs projetados naquele padrão conseguem executar. Quanto mais fácil for programar em alto nível, mais complexo — e caro — é o desenvolvimento do hardware, e vice-versa.

- O que é a tecnologia Intel Foveros?

- 7 Empresas que já fizeram processadores e você não lembra

Cada uma foi desenvolvida para contornar barreiras específicas para o avanço da computação, ao longo de 50 anos elas aproveitaram conceitos uma da outra, mas alguns elementos básicos de seus projetos originais. O Canaltech conversou com Pietro Colloca, Engenheiro da Intel especialista em IA e IoT, para pontuar suas especificidades e auxiliar a identificar cada uma delas mesmo em um eventual futuro “híbrido”.

“Tanto RISC quanto CISC são chamados de ISA, Instruction Set Architecture. É basicamente um padrão desenhado para a gente definir como é que o computador vai acabar funcionando”, pontuou o especialista da Intel.

–

Siga no Instagram: acompanhe nossos bastidores, converse com nossa equipe, tire suas dúvidas e saiba em primeira mão as novidades que estão por vir no Canaltech.

–

Complexidade e tamanho de instruções

A primeira diferença relevante entre computadores em CISC e RISC é, naturalmente, a complexidade e tamanho das instruções. Enquanto máquinas RISC dependem de instruções simples e com tamanhos pré-determinados, processadores CISC utilizam instruções muito mais complexas, transformando comandos básicos em instruções incorporadas a comandos mais complexos.

Uma operação básica de soma em RISC, por exemplo, envolveria comandos independentes para carregar dados em diferentes registradores, realizar a soma dos valores e carregar o resultado no registrador de destino. Já em CISC, o comando “SOMAR 2 e 5” traz todas as instruções intermediárias em apenas uma linha de código.

Complexidade de hardware × simplicidade do código

Os computadores CISC foram desenvolvidos para facilitar a programação de aplicações, e por isso foram adicionando novos componentes cada vez mais especializados a cada geração. Ao tornar o hardware altamente complexo e com uma série de coprocessadores incorporados ao silício, é possível também incorporar instruções menores como etapas pré-programadas de instruções maiores e mais complexas.

Por essa razão, executar uma simples operação de soma em RISC exige múltiplas linhas de código, enquanto em CISC ela exige apenas uma. Esse mesmo raciocínio vale para todas as outras operações computacionais, como inferências, condições, fluxo de informações e operações lógicas.

“Quebrando um pouquinho mais sobre o CISC, por mais que ele tenha esse ‘complexo’ no nome, a vinda é para facilitar. Dentro da arquitetura em si, ela tem diversos sets de instruções, que são basicamente as operações matemáticas que o computador consegue executar. Em vez de em uma arquitetura RISC você escrever ‘eu gostaria que você carregasse essa informação no registrar A, carregasse essa informação no registrador B, e realizar a multiplicação’, a gente só coloca ‘multiplicação’ e o processador realiza a operação completa”, explica Colloca à reportagem do Canaltech.

Sendo assim, quanto mais complexo o hardware, mais complexas podem ser as operações, e mais simples é programar para aquele sistema. Em contrapartida, a complexidade demasiada torna o processo de fabricação relativamente mais caro, difícil, e sua operação costuma consumir muito mais energia.

Adotar a arquitetura RISC, por exigir uma sintaxe mais próxima da linguagem de máquina, irá implicar em códigos de software extremamente complexos, mais longos e detalhados.

Memória × Registradores

Por não possuir aceleradores especializados, todas as instruções em RISC são executadas diretamente pelo processador. Para dar conta de realizar todos os comandos da arquitetura, o projeto de CPUs em RISC exige um número muito maior de registradores físicos, uma vez que operações interdependentes precisam carregadas em paralelo para serem realizadas ineditamente após a execução de um comando anterior.

Em CISC o mesmo não ocorre, pois todas as operações de uma instrução mais complexa são carregadas e executadas diretamente na memória do sistema, apenas com os resultados sendo armazenados para os registradores. Por essa razão, processadores RISC precisam de menos memória, mas muito mais registradores, enquanto em CISC a proporção é inversa.

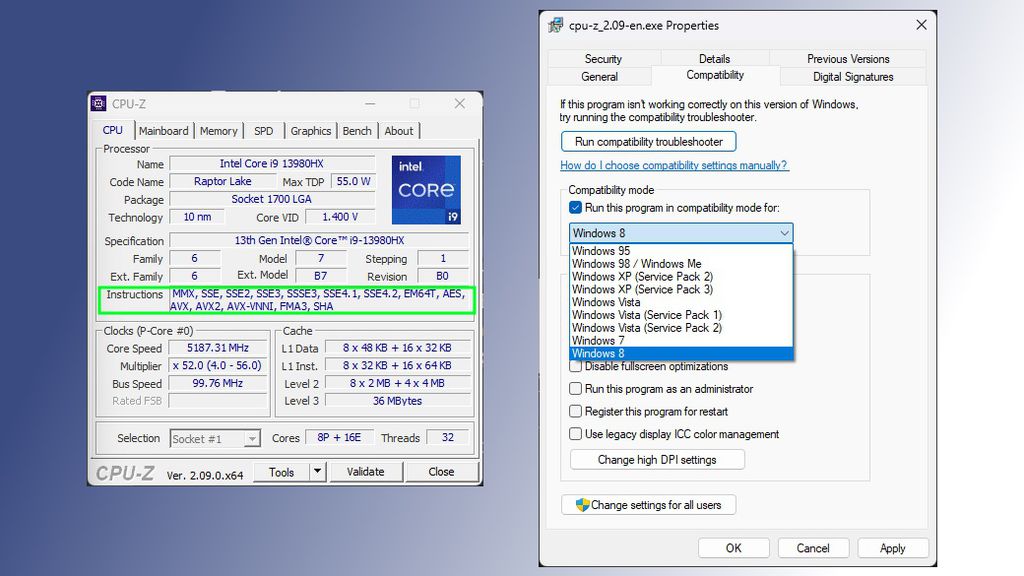

Um processador Intel Core i9-10900k, por exemplo, conta com 16 registradores de instruções únicas e dados múltiplos (SIMD), com cada núcleo de hyperthread também trazendo 16 registradores SIMD. Processadores ARM, de maneira geral, podem ter entre 32 e 192 registradores por núcleo dependendo do projeto.

Acesso à memória

Como todas as instruções em RISC são executadas imediatamente no nível dos registradores, além de o sistema depender menos de memória, o processador não precisa de acesso direto à memória. A diferença é uma das vantagens dos processadores ARM no quesito eficiência, uma vez que as velocidades de memória costumam ser bem inferiores às da CPU.

Por não depender de carregar e executar instruções em componentes mais lentos, processadores RISC costumam consumir bem menos energia. Isto é ideal para sistemas embarcados de baixo consumo, como dispositivos de IoT, smartphones ou mesmo servidores onde cada Watt faz diferença no custo total de operação (TCO).

Ciclos computacionais

Quando falamos de frequência de CPUs, na verdade, estamos descrevendo quantos ciclos computacionais são realizados em um segundo. Um processador com clock base de 2,9 GHz, por exemplo, realiza 2,9 bilhões de ciclos por segundo, com os valores podendo passar de 5 bilhões de ciclos em atividades intensas.

Por essa razão, as execuções em ciclos únicos do RISC estão entre as principais métricas para justificar em quais tipos de uso a arquitetura é mais vantajosa. Resumidamente, por trabalhar com menos conjuntos de instruções, e instruções muito mais simples, cada uma delas é sempre executada em apenas um ciclo, ou seja, um CPU RISC operando em 2,8 GHz executa 2,8 bilhões de instruções por segundo.

Em CISC, isso muda bastante de figura, principalmente porque as instruções têm tamanhos variáveis. Algumas delas podem ser executadas em apenas um ciclo, mas a maioria exige múltiplos ciclos para serem executadas.

Por essa razão a Intel implementou nos novos processadores x86 o padrão de núcleos híbridos big.LITTLE, com alguns voltados para execuções simples, e outros para execuções complexas. Efetivamente, comandos mais próximos do nível de máquina e que podem ser executados em ciclos únicos, mesmo em CISC, são direcionados para os núcleos de eficiência (E-core), enquanto o restante dos comandos é processado pelos núcleos de desempenho (P-core).

Retrocompatibilidade

Outra vantagem inerente da arquitetura CISC é que não é preciso alterar os microcódigos originais a cada nova geração de processadores, pois a maioria deles está embarcada nos aceleradores. Dessa forma, todo processador x86 moderno já possui a capacidade de executar os mesmos códigos de máquinas antigas.

“[A Intel] trouxe a arquitetura x86 em 1978, com o 8086, e conforme a gente foi avançando, a gente foi colocando coisa, como os nossos aceleradores: o MMX, o SSE, o AVX2 e por aí vai. Isso é justamente para simplificar as operações matemáticas [no nível do hardware]. A gente utiliza dos aceleradores para facilitar a escrita e execução dos códigos”, explica o especialista da Intel.

Em RISC, para garantir o mínimo possível de instruções, cada geração precisa ser reprogramada até certo ponto, removendo microcódigos antigos para inserir novos. Isso faz com que a maioria dos processadores RISC não sejam intercompatíveis, e sejam projetados especificamente para suas funções.

Uma CPU ARM Amazing-Grace da NVIDIA, especializada em operações de inferência para IA, não tem as mesmas instruções de um processador Apple ARM M2, por exemplo. Apesar de serem dois produtos RISC extremamente avançados e topo de linha para seus segmentos, eles não conseguem realizar nativamente as mesmas tarefas um do outro.

Arquiteturas complementares

Na prática, CISC e RISC foram desenvolvidas em momentos diferentes para resolver limitações computacionais diferentes. No entanto, ambas evoluíram lado a lado, absorvendo as melhorias uma da outra sempre que possível.

“[Nas CPUs Intel] são duas arquiteturas x86 diferentes, a Golden Cove e a Gracemont são focadas em propósitos diferentes, enquanto o P-Core vai ter habilidades como hyperthreading, o E-Core é voltado para ter uma eficiência maior. [Comparando os big.LITTLE ARM e x86] o conceito pode ser parecido, mas na hora de montar não é a mesma coisa”, pontua Pietro Colloca.

O exemplo da arquitetura big.LITTLE, é inclusive o principal desses casos, pois foi adotado inicialmente por processadores ARM para smartphones, e foi adotado pela Intel desde os chips Alder Lake. Em paralelo, os processadores ARM M1, M2 e M3 da Apple, ainda utilizam arquitetura RISC, mas possuem quase tantos transistores quanto CPUs x86 em CISC, e também trabalham com conjuntos de instruções mais complexas para facilitar a programação na plataforma.

A tendência é que cada vez mais as duas arquiteturas se combinem, com o ponto-chave para diferenciá-las sendo mais uma questão de publicidade do que, de fato, especificações técnicas.

- 🛒 Compre processadores AMD pelo melhor preço!

- 🛒 Compre processadores Intel pelo melhor preço!

Leia a matéria no Canaltech.

Trending no Canaltech:

- Popó x Kleber Bambam | Como assistir à luta ao vivo?

- Cromossomo Y está desaparecendo da espécie humana

- Presença de chumbo em copo Stanley rende processos à empresa

- 10 comandos legais para usar no Gemini

- Os 10 filmes mais vistos da semana (24/02/2024)

- Artigo científico com imagens esdrúxulas de IA é retirado do ar